Brain‑Inspired Neuro‑Synaptic Chips: The Next‑Gen AI Revolution for Human‑Like Energy Efficiency

Brain‑inspired neuro‑synaptic chips are rapidly becoming the cornerstone of next‑generation artificial intelligence. By mimicking the way biological neurons and synapses work, these chips promise to deliver high performance while consuming a fraction of the power required by traditional von Neumann architectures. In this article, we explore the science behind neuro‑synaptic design, the key advantages they bring, and how they could reshape industries from autonomous vehicles to mobile computing.

1. The Neuroscience Behind the Technology

Unlike conventional processors that separate memory and computation, the human brain integrates both functions within the same synaptic structures. Each synapse acts as a dynamic, programmable resistor that can strengthen or weaken connections through plasticity. Neuro‑synaptic chips replicate this behavior with crossbar arrays, memristive devices, and spiking neural networks (SNNs). The result is an architecture where data is processed on‑the‑fly, drastically reducing data movement and, consequently, energy consumption.

1.1 Memristive Crossbars: The Core Building Block

- Non‑Volatile Memory: Memristors retain state without power, enabling persistent synaptic weights.

- High Density: Crossbar arrays can pack thousands of synapses into a single chip area, rivaling biological neuron densities.

- Analog Computation: Current‑mode operations allow for efficient multiply‑accumulate operations integral to neural inference.

1.2 Spiking Neural Networks: Emulating Temporal Dynamics

While traditional deep learning relies on continuous activation functions, SNNs process information as discrete spikes over time. This event‑driven computation reduces idle cycles, letting the chip idle between spikes and save power. Moreover, SNNs naturally support online learning and adaptive behaviors—key attributes for autonomous systems that must react to changing environments in real time.

2. Energy Efficiency: From Gigawatts to Milliwatts

One of the most compelling claims of brain‑inspired chips is their potential to reach human‑like energy efficiency. The human brain consumes roughly 20 W of power to perform a myriad of tasks—vision, language, motor control—yet achieves what would take classical computers terawatts. Neuro‑synaptic chips aim to close this gap by eliminating costly memory‑to‑compute transfers.

- 0.1–1 W for inference: Early prototypes demonstrate real‑time image classification on sub‑watt power budgets.

- Ultra‑low standby: Memristive devices require no leakage current when idle, preserving battery life in portable devices.

- Scalability: As device dimensions shrink, power density remains constant or decreases, allowing larger networks without proportional power penalties.

3. Real‑World Applications

3.1 Autonomous Vehicles

Onboard AI must process sensor streams (LIDAR, cameras, radar) in milliseconds while keeping power budgets tight for long‑range electric vehicles. Neuro‑synaptic chips can perform simultaneous perception, prediction, and control tasks with minimal energy, extending driving range and reducing thermal loads.

3.2 Mobile and Edge Devices

Smartphones, wearables, and industrial IoT sensors all benefit from compact, low‑power AI. Deploying neuro‑synaptic chips in these platforms enables advanced features—real‑time speech translation, augmented reality, or predictive maintenance—without draining batteries or relying on cloud off‑loading.

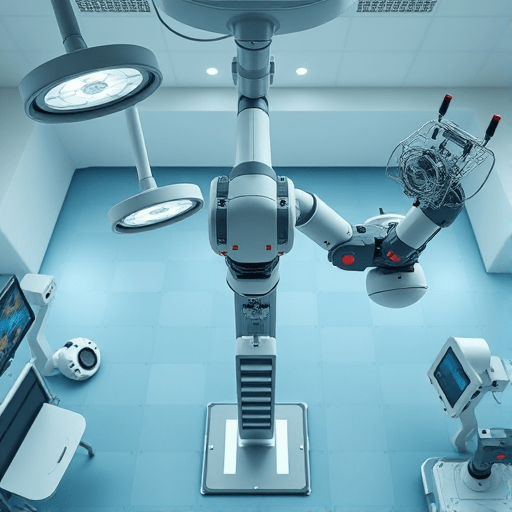

3.3 Healthcare and Brain‑Computer Interfaces

Brain‑inspired hardware aligns seamlessly with neural data streams, facilitating high‑bandwidth, low‑latency interfaces for prosthetics, neurofeedback, and diagnostic imaging. Moreover, the low power draw is essential for implantable devices where heat dissipation is a critical safety concern.

4. Challenges and the Road Ahead

Despite the promise, several hurdles remain before neuro‑synaptic chips can replace conventional processors in mainstream applications.

- Device Variability: Memristors exhibit stochastic behavior and drift over time, necessitating robust calibration and error‑tolerant algorithms.

- Programming Models: Current deep‑learning frameworks assume dense, floating‑point tensors; adapting them to sparse, spiking networks requires new software stacks.

- Manufacturing Scale: Producing consistent, defect‑free crossbar arrays at commodity yields is still a significant engineering challenge.

- Standardization: Industry‑wide benchmarks and evaluation protocols are needed to compare neuro‑synaptic solutions fairly against traditional accelerators.

5. The Ecosystem: Companies and Research Groups Leading the Charge

Numerous startups and academic labs are pushing the boundaries of neuro‑synaptic technology. Companies like Cerebras Systems, SynSense, and BrainChip are delivering early‑stage prototypes, while universities such as MIT, Stanford, and the University of Cambridge are publishing foundational research. Partnerships between hardware vendors, AI software developers, and end‑user industries will accelerate commercialization.

6. Future Outlook: From Specialized Co‑Processors to System‑On‑Chip Integration

Initially, brain‑inspired chips will serve as accelerators alongside traditional CPUs and GPUs. However, as fabrication maturity improves and software ecosystems mature, these chips could become the core of system‑on‑chip (SoC) solutions. In such a scenario, a single silicon die would host both conventional logic for control and specialized neuro‑synaptic arrays for AI workloads, achieving unprecedented integration density and energy savings.

7. Practical Tips for Engineers Looking to Adopt Neuro‑Synaptic Hardware

- Start with Simulation: Use open‑source SNN simulators (e.g., Brian, NEST) to prototype algorithms before hardware deployment.

- Leverage Transfer Learning: Pre‑train models on GPU clusters, then fine‑tune on neuro‑synaptic hardware to mitigate device variability.

- Adopt Mixed‑Precision: Combine low‑precision spiking inference with occasional high‑precision refinement stages for accuracy‑critical tasks.

- Engage with Standards Bodies: Participate in IEEE and other standards groups to influence interface specifications and benchmark suites.

Conclusion

Brain‑inspired neuro‑synaptic chips are poised to redefine artificial intelligence by offering human‑like energy efficiency without compromising computational prowess. While challenges in device variability, programming models, and manufacturing remain, the accelerating pace of research and industry collaboration suggests that these chips will transition from laboratory curiosities to mainstream solutions within the next decade. As the AI landscape evolves, staying informed about neuro‑synaptic developments will be essential for innovators seeking sustainable, high‑performance computing.

Discover how neuro‑synaptic technology can power your next AI project—contact our team today.